- News

- 1 min read

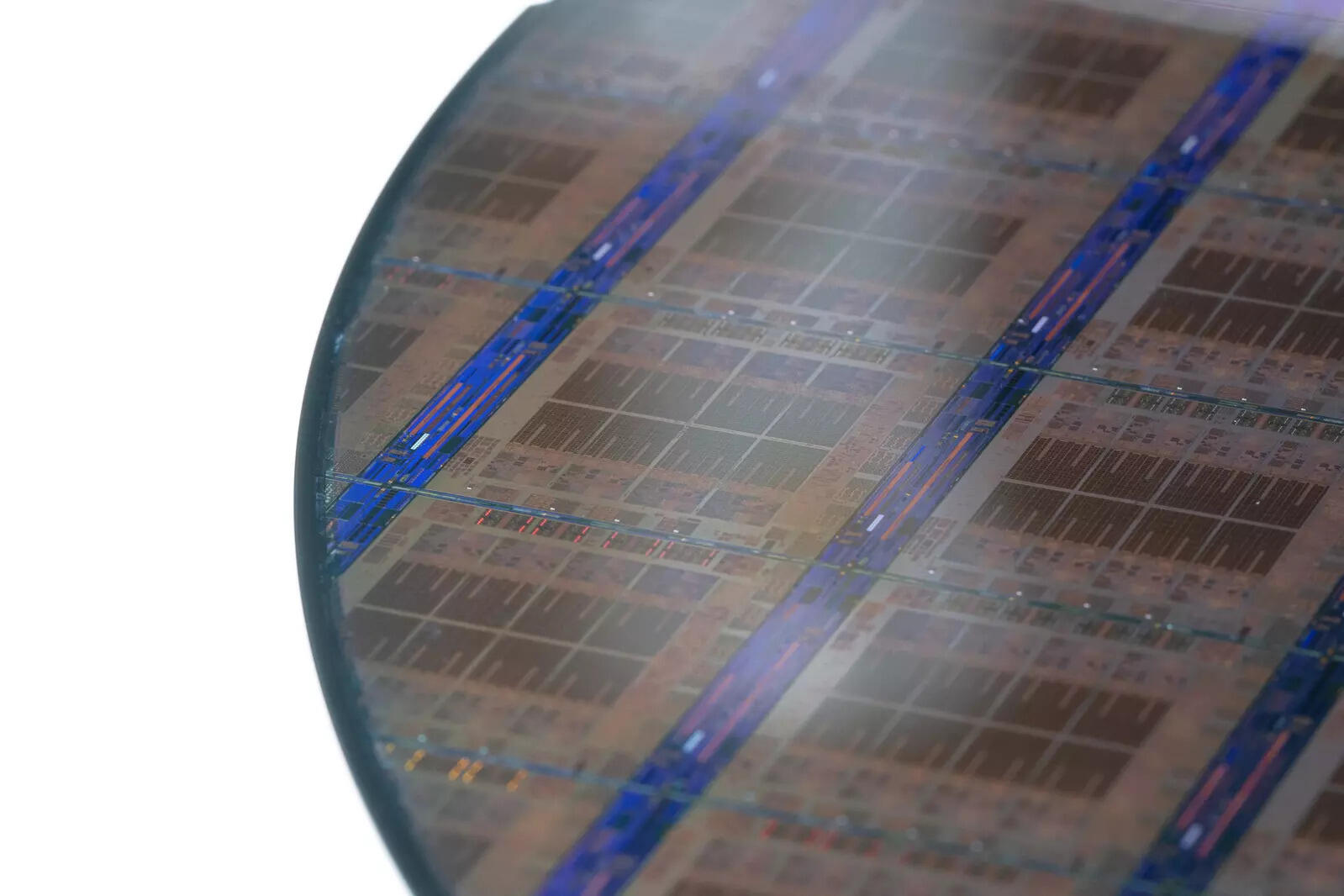

IBM's new processor to detect fraud in real-time

Tech giant IBM on Tuesday unveiled details of the upcoming new IBM Telum Processor, designed to bring deep learning inference to enterprise workloads to help address fraud in real-time.

BENGALURU: Tech giant IBM on Tuesday unveiled details of the upcoming new IBM Telum Processor, designed to bring deep learning inference to enterprise workloads to help address fraud in real-time.

Telum is IBM's first processor that contains on-chip acceleration for AI inferencing while a transaction is taking place.

"The newly launched IBM Telum, Z Series chip is designed to cater to the volume, while enabling applications to run efficiently where their data resides. The chip will also allow businesses to capture insights and fight fraud in real-time," Ravi Jain, Director - Server Sales, India South Asia, said in a statement.

According to the company, the new chip design unlocks the ability to leverage deep learning inferencing on high-value transactions, designed to greatly improve the ability to intercept fraud, among other use cases.

It features an innovative centralised design, which allows clients to leverage the full power of the AI processor for AI-specific workloads, making it ideal for financial services workloads like fraud detection, loan processing, clearing and settlement of trades, anti-money laundering and risk analysis.

With these innovations, clients will be positioned to enhance existing rules-based fraud detection or use machine learning, accelerate credit approval processes, improve customer service and profitability, identify which trades or transactions may fail, and propose solutions to create a more efficient settlement process.

The chip contains 8 processor cores with a deep super-scalar out-of-order instruction pipeline, running with more than 5GHz clock frequency, optimized for the demands of heterogeneous enterprise-class workloads.

The completely redesigned cache and chip-interconnection infrastructure provides 32MB cache per core and can scale to 32 Telum chips. The dual-chip module design contains 22 billion transistors and 19 miles of wire on 17 metal layers.

COMMENTS

All Comments

By commenting, you agree to the Prohibited Content Policy

PostBy commenting, you agree to the Prohibited Content Policy

PostFind this Comment Offensive?

Choose your reason below and click on the submit button. This will alert our moderators to take actions